# **Preliminary**

March 1997

S3 Incorporated P.O. Box 58058 Santa Clara, CA 95052-8058

#### NOTATIONAL CONVENTIONS

The following notational conventions are used in this data book:

Signal names are shown in all uppercase letters. For example, XD.

A bar over a signal name indicates an active low signal. For example,  $\overrightarrow{OE}$

n-m indicates a bit field from bit n to bit m. For example, 7-0 specifies bits 7 through 0, inclusive.

n:m indicates a signal (pin) range from n to m. For example D[7:0] specifies data lines 7 through 0, inclusive

Use of a trailing letter H indicates a hexadecimal number. For example, 7AH is a hexadecimal number.

Use of a trailing letter b indicates a binary number. For example, 010b is a binary number.

When numerical modifiers such as K or M are used, they refer to binary rather than decimal form. Thus, for example, 1 KByte would be equivalent to 1024, not 1,000 bytes.

#### NOTICES

© Copyright 1997 S3 Incorporated. All rights reserved. If you have received this document from S3 Incorporated in electronic form, you are permitted to make the following copies for business use related to products of S3 incorporated: one copy onto your computer for the purpose of on-line viewing, and one printed copy. With respect to all documents, whether received in hard copy or electronic form, other use, copying or storage, in whole or in part, by any means electronic, mechanical, photocopying or otherwise, is not permitted without the prior written consent of S3 Incorporated, P.O. Box 58058, Santa Clara C4 95062-8058. S3, True Acceleration and ViRGE are registered trademarks of S3 Incorporated. The S3 Corporate Logo. S3 on Board, S3 on Board design, S3d design, Trio, Trio64V+, Trio64V2/DX, Trio64V2/GX, Plato, S3d, Scenic, Scenic Highway, Sonic, SonicVibes, S35, S3FM. InfiniPatch, InfiniBate, Audio Card on a Chip, QuickRamp, Aurora64V+, DuoView, Streams Processor, Galileo, No Compromise Integration, No Compromise Acceleration and Innovations in Acceleration are trademarks of S3 Incorporated. Other trademarks referenced in this document are owned by their respective companies. The material in this document is for information only and is subject to change without notice. S3 Incorporated reserves the right to make changes in the product design without reservation and without notice to its users.

Additional information may be obtained from:

S3 Incorporated, Literature Department P.O. Box 58058, Santa Clara, CA 95052-8058.

Telephone: 408-980-5400, Fax: 408-980-5444

# **Table of Contents**

| List of Figures v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5.3 AUDIO CONTROL INTERFACES 5-6                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5.3.1 Analog Audio Control Interfaces 5-6                               |

| List of Tables vi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5.3.2 Hardware Master Volume Control<br>Interface (Up/Down Button       |

| Section 1: Introduction 1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Support) 5-7<br>5.3.3 MPU-401-COMPATIBLE MIDI                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | UART Interface 5-7                                                      |

| Section 2: Mechanical Data 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.3.3.1 MIDI UART Registers 5-7                                         |

| 2.1 THERMAL SPECIFICATIONS 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.3.3.2 MIDI UART Operation 5-9                                         |

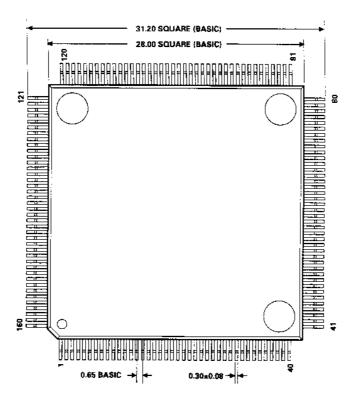

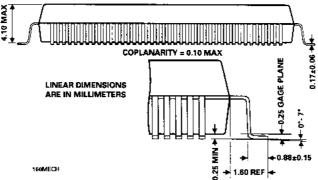

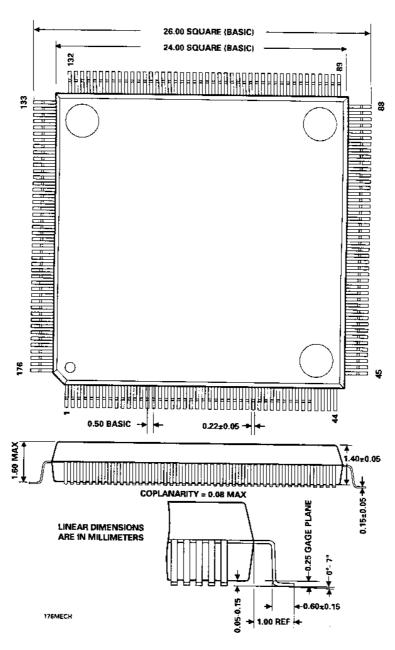

| 2.2 MECHANICAL DIMENSIONS 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5.3.4 Game Port/Joystick Timer                                          |

| 2.2 MESTATIONE DIVIENSIONS 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Interface 5-10                                                          |

| C41 0- B'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5.3.4.1 Game Port Register 5-10                                         |

| Section 3: Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5.3.4.2 Game Port Speed                                                 |

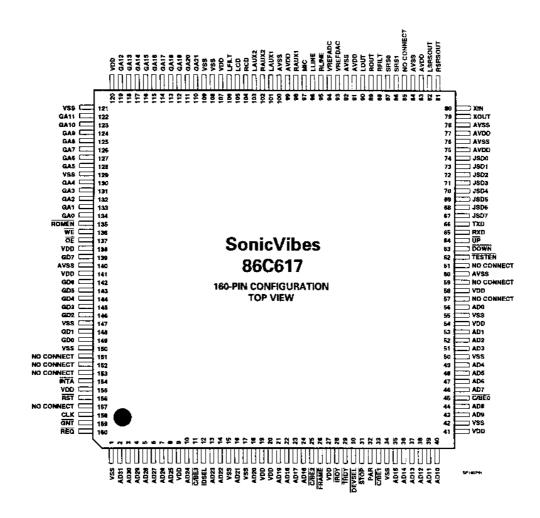

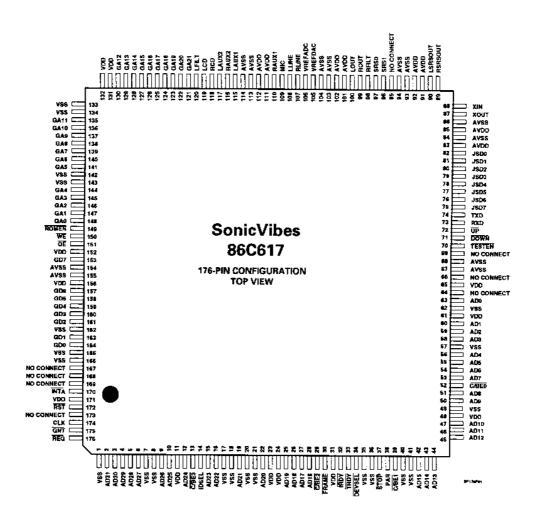

| 3.1 PINOUT DIAGRAMS 3-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Compensation 5-11                                                       |

| 3.2 PIN DESCRIPTIONS 3-4 3.3 PIN LISTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                         |

| 3.3 PIN LISTS 3-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Section 6: Audio Control 6-1                                            |

| <b>_</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6.1 SOUND BLASTER PRO GAMES                                             |

| Section 4: Electrical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | COMPATIBILITY 6-1                                                       |

| Characteristics 4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6.1.1 Games Compatible Registers . 6-1.                                 |

| 4.1 MAXIMUM RATINGS 4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6.1.2 Games Compatibility Issues . 6-2                                  |

| 4.2 POWER DISSIPATION 4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6.2 S3FM SYNTHESIS 6-2                                                  |

| 4.3 DC CHARACTERISTICS 4-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6.3 ENHANCED MODE 6-3                                                   |

| 4.4 AC CHARACTERISTICS 4-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6.3.1 Wavetable Synthesis 6-3                                           |

| 4.5 AC TIMING 4-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6.3.2 PCM Playback and Record 6-3                                       |

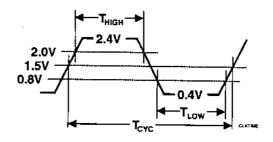

| 4.5.1 Clock Waveform Timing 4-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6.3.3 CODEC/Mixer Operation 6-4<br>6.3.4 SRS 3D Audio Enhancement . 6-4 |

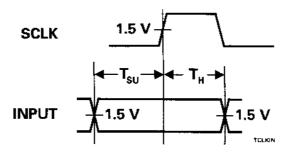

| 4.5.2 Input Timing 4-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6.3.4 SRS 3D Audio Enhancement . 6-4                                    |

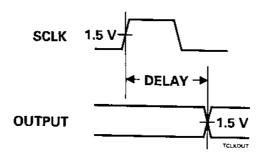

| 4.5.3 Output Timing 4-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>.</b>                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Section 7: Enhanced Mode                                                |

| Section 5: Hardware Interfaces 5-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Registers                                                               |

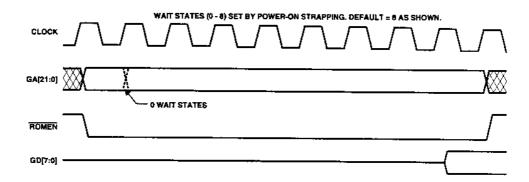

| 5.1 POWER-ON STRAPPING 5-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7.1 DIRECT ACCESS CODEC/MIXER                                           |

| 5.2 PCI BUS INTERFACE 5-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | REGISTER DESCRIPTIONS 7-1                                               |

| 5.2.1 PCI Configuration 5-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7.2 INDEXED CODEC/MIXER REGISTER                                        |

| 5.2.2 PCI External Memory Interfaces 5-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DESCRIPTIONS 7-6                                                        |

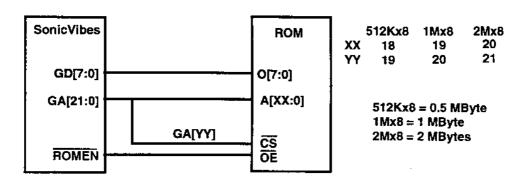

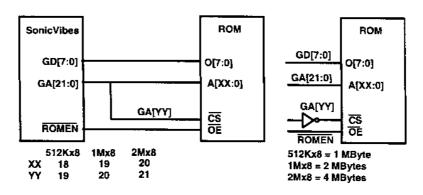

| 5.2.2.1 ROM Interface 5-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                         |

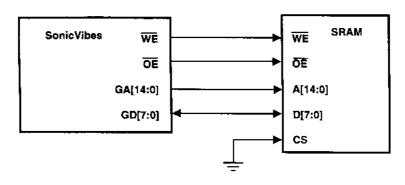

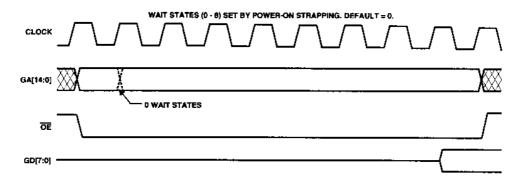

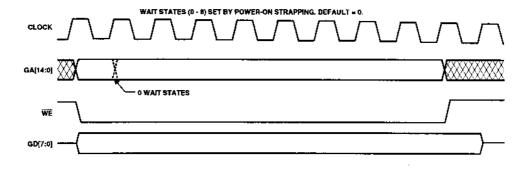

| 5.2.2.2 SRAM Interface 5-3 5.2.3 Distributed DMA Support 6-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Section 8: PCI Registers 8-1                                            |

| End and and and analytic control of the control of |                                                                         |

| 5.2.4 PCI PnP Issues 5-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                         |

PRELIMINARY

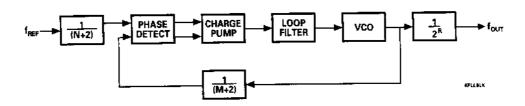

| Appe | ndix A: Clock Synthesis and |     |

|------|-----------------------------|-----|

| Powe | r Management                | A-1 |

| A.1  | CLOCK SYNTHESIS             | A-  |

| A.2  | POWER MANAGEMENT            | A-: |

# **List of Figures**

| #   | Tial -                   |                        |

|-----|--------------------------|------------------------|

| #   | Title P                  | age                    |

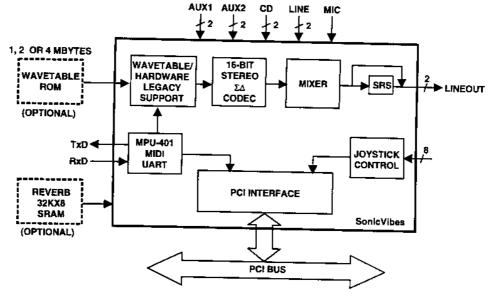

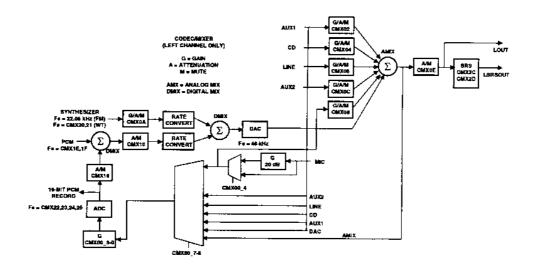

| 1-1 | System Block Diagram     | 1-3                    |

| 2-1 | 160-pin PQFP Mechanical  |                        |

|     | Dimensions               | 2-2                    |

| 2-2 | 176-pin TQFP Mechanical  |                        |

|     | Pa.* .                   | 2-3                    |

| 3-1 | 160-pin Package Pinout   | 3-2                    |

| 3-2 | 176-pin Package Pinout   | 3-3                    |

| 4-1 |                          | 4-5                    |

| 4-2 |                          | 4-6                    |

| 4-3 |                          | 4-7                    |

| 5-1 |                          | 5-2                    |

| 5-2 |                          | 5-3                    |

| 5-3 | DOM Decide Common Agents | 5-3                    |

| 5-4 | CDANII-44                | 5-4                    |

| 5-5 |                          | 5-4                    |

| 5-6 | CDASSISTE AS SELECTION   | 5-4                    |

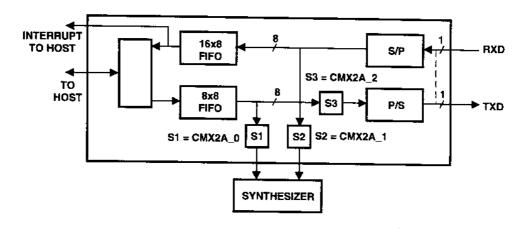

| 5-7 | MAIDLE CADT DE LA DE     | 5-9                    |

| 6-1 |                          | 5- <del>3</del><br>5-4 |

| A-1 |                          | \-2                    |

|     |                          | 4-2                    |

# **List of Tables**

| # Title Page # Title                                                  | Page           |

|-----------------------------------------------------------------------|----------------|

| 3-1 Pin Descriptions 3-4 5-6 Game Port Register                       | 5-10           |

| 3-2 Alphabetical Pin Listing 3-7 6-1 Games Compatible Direct          | t Access       |

| 3-3 Numerical Pin Listing 3-9 Registers                               | <i>.</i> 6-1   |

| 4-1 Maximum Ratings 4-1 6-2 Games Compatible Mixel                    | r (Indexed)    |

| 4-2 Operational Power Dissipation . 4-1 Registers                     | 6-2            |

| 4-3 Analog Input DC Characteristics . 4-2 6-3 Mixer Input Naming Con- | ventions 6-2   |

| 4-4 Analog Output DC Characteristics 4-2 6-4 S3FM Registers           | 6-3            |